CHERIoT Technology +

Intellectual Property

CHERIoT Overview

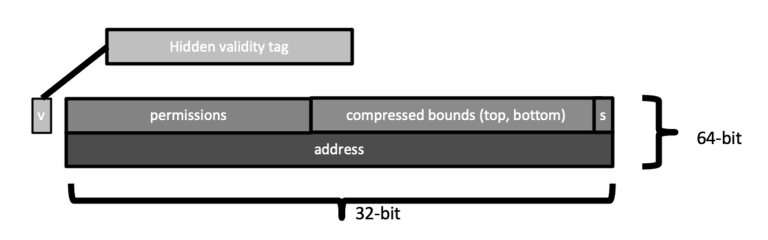

The Capability Hardware Extension to RISC-V for IoT (CHERIoT) platform was originally developed at Microsoft and is now part of an effort spanning multiple companies. It builds on top of CHERI to provide a solid foundation for secure embedded devices. CHERI provides referential integrity (pointers cannot be forged), spatial memory safety (pointers carry bounds that cannot be extended), call gates, and so on.

CHERIoT extends this with a complete platform providing deterministic use-after-free protection, a lightweight compartment model, lexically-scoped delegation of objects across compartment calls, and many more benefits.

The CHERIoT project comprises several repositories:

- The formal model of the CHERIoT ISA. This is used to build an executable simulator and to prove properties of both the ISA and of implementations. The current (draft) version of the specification is built in CI.

- The CHERIoT RTOS, a clean-slate RTOS designed to take advantage of CHERIoT features. This provides the compartment model, a heap that can be safely shared across mutually distrusting compartments, and a host of other features.

- CHERIoT LLVM provides the toolchain for building the RTOS and other software that runs atop it.

- CHERIoT-Audit provides tooling for auditing the isolation properties of CHERIoT firmware images.

- The CHERIoT Ibex, an area-optimised core that implements the ISA. This is very slightly larger than the Ibex with a 16-element Physical Memory Protection unit, yet provides object-granularity memory safety and scales to a number of compartments bounded only by available memory.

- The CHERIoT small and fast FPGA emulator platform. This provides a set of peripherals such as a UART and interrupt controllers that provide a minimal useful integration of the Ibex.

The CHERIoT dev container includes the toolchain, the simulator built from the formal model, and a verilator simulation of the Ibex. This can be used explicitly via Docker / Podman or by opening the RTOS repository in Visual Studio Code or another editor that supports dev containers.

SCI Semiconductor is a strong proponent of Open Source technology, believing that it both delivers both the opportunity to rapidly grow and thrive in a permissive ecosystem, and avoids the trap of maintaining proprietary commercial technologies.

SCI activly manages and maintains multiple repos on GitHub, including in partneship with Microsoft the management of the CHERIoT core. We also mirror development activities to our https://cheriot.org website and signal channels.

CHERIoT Capability replaces traditional pointer structures

ICENI System

Intellectual Property

SCI are committed to open source and maintaining the permissiveness of the CHERIoT core, software and ecosystem. However in the development of our ICENI family of devices certain commercial differentiation has had to be evolved to meet the specific needs of the marketplace, especially for critical infrastructure, defense, and telecoms.

In order to continue to deliver ICENI and other solutions critical Intellectual Property has been evolved and registerd, which we believe significantly enhances the solutions and delivers outstanding power and perfromance improvements.

System on Chip Engagements

ICENI devices are ideal for a wide array of applications in multiple markets.

However wit is clear that that this type of device is not always best suited for high performance applications where a fully integrated system on chip (SoC) is required

SCI recommend SoC vendors thoroughly investigate the open source components of the CHERIoT ecosystem, but we are pleased to offer specific accelerators, system IP , and fully integrated processor systems that may support a faster time to market and enhanced software ecosystem support.

Please contact SCI Semiconductors for more information at info@scisemi.com

We need your consent to load the translations

We use a third-party service to translate the website content that may collect data about your activity. Please review the details in the privacy policy and accept the service to view the translations.